Verilog assign StatementAssign statements are used to drive values on the net. And it is also used in Data Flow Modeling. Signals of type wire or a data type require the continuous assignment of a value. As long as the +5V battery is applied to one end of the wire, the component connected to the other end of the wire will get the required voltage. This concept is realized by the assign statement where any wire or other similar wire (data-types) can be driven continuously with a value. The value can either be a constant or an expression comprising of a group of signals. Syntax The assignment syntax starts with the keyword assign, followed by the signal name, which can be either a signal or a combination of different signal nets. The drive strength and delay are optional and mostly used for dataflow modeling than synthesizing into real hardware. The signal on the right-hand side is evaluated and assigned to the net or expression of nets on the left-hand side. Delay values are useful for specifying delays for gates and are used to model timing behavior in real hardware. The value dictates when the net should be assigned with the evaluated value. RulesSome rules need to be followed during the use of an assign statement:

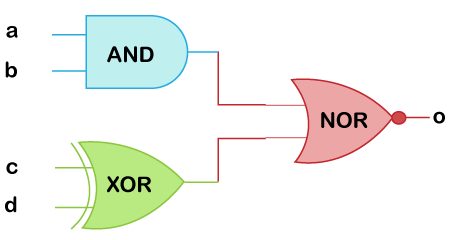

Assign reg VariablesWe cannot drive or assign reg type variables with an assign statement because a reg variable is capable of storing data and is not driven continuously. Reg signals can only be driven in procedural blocks such as always and initial. Implicit Continuous AssignmentWhen an assign statement is used to assign the given net with some value, it is called an explicit assignment If an assignment to be done during the net is declared, it is called an implicit assignment. Combinational Logic DesignConsider the following digital circuit made from combinational gates and the corresponding Verilog code.

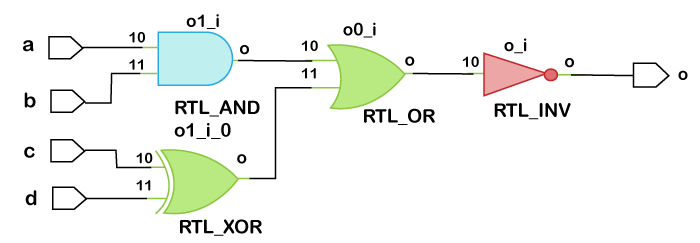

Combinational logic requires the inputs to be continuously driven to maintain the output, unlike sequential elements like flip flops where the value is captured and stored at the edge of a clock. An assigned statement satisfies the purpose because the output o is updated whenever any of the inputs on the right-hand side change. Hardware SchematicAfter design elaboration and synthesis, a combinational circuit behaves the same way as modeled by the assign statement.

The signal o becomes 1 whenever the combinational expression on the RHS becomes true. Similarly, o becomes 0 when RHS is false. Output o is X from 0ns to 10ns because inputs are X during the same time.

Next TopicVerilog Operators

|

For Videos Join Our Youtube Channel: Join Now

For Videos Join Our Youtube Channel: Join Now

Feedback

- Send your Feedback to [email protected]

Help Others, Please Share