Verilog Initial BlockThe always block indicates a free-running process, but the initial block indicates a process executes exactly once. Both constructs begin execution at simulator time 0, and both execute until the end of the block. Initial blocks can be used in either synthesizable or non-synthesizable blocks. They are commonly used in test benches. Initial blocks cause particular instructions to be performed at the beginning of the simulation before any other instructions operate. Initial blocks only operate once. A synthesizable initial block is used to set the power-on value of registers, RAM, and ROM within FPGAs. However, initial blocks cannot be synthesized in ASICs or CPLDs. Initial and always block describe independent processes, which means the statements in one process execute autonomously. Both types of processes consist of procedural statements, and both start immediately as the simulator is started. The main differences between them are:

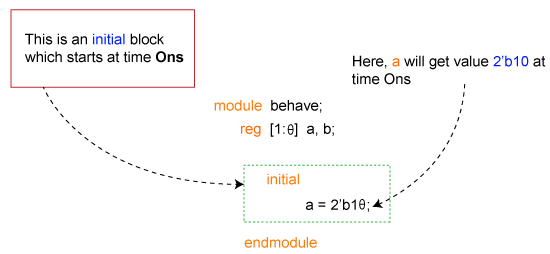

Syntax Verilog initial block follows the following syntax: Initial block usesAn initial block is not synthesizable and cannot be converted into a hardware schematic with digital elements. The initial blocks do not have more purpose than to be used in simulations. These blocks are primarily used to initialize variables and drive design ports with specific values. Initial Block ExecutionAn initial block is started at the beginning of a simulation at time 0 unit. This block will be executed only once during the entire simulation. Execution of an initial block finishes once all the statements within the block are executed, as shown in the following image.

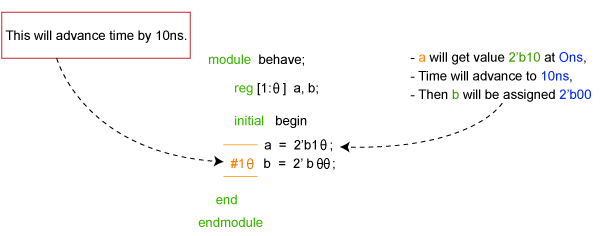

The image shown above has a module called behave, which has a and b internal signals. The initial block has only one statement, and hence it is not necessary to place the statement within begin and end. This statement assigns the value 2'b10 to a when the initial block is started at time 0 units. Initial Block Delay ElementThe code shown below has an additional statement that assigns some value to the signal b. However, this happens only after 10-time units from the execution of the previous statement. For example, If a is assigned first with the given value and then after 10-time units, b is assigned to 0.

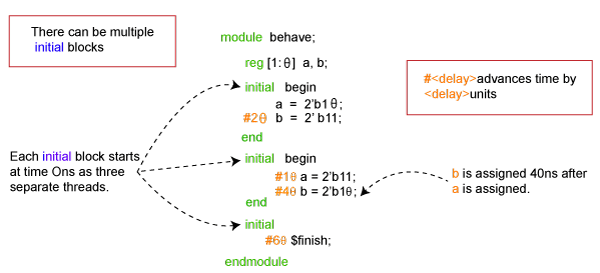

Initial Blocks in a moduleThere are no limits to the number of initial blocks that can be defined inside a module. The code shown below has three initial blocks, all of which are started at the same time and run in parallel. However, depending on the statements and the delays within each initial block, the time taken to finish the block may vary.

NOTE: $finish is a Verilog system task that tells the simulator to terminate the current simulation.In the above image, the first block has a delay of 20 units, while the second has a total delay of 50 units (10 + 40), and the last block has a delay of 60 units. Hence the simulation takes 60-time units to complete since there is atleast one initial block still running until 60-time units. If the last block had a delay of 30-time units, as shown below, the simulation would have ended at 30-time units, thereby killing all the other initial blocks that are active at that time.

Next TopicVerilog Block Statements

|

For Videos Join Our Youtube Channel: Join Now

For Videos Join Our Youtube Channel: Join Now

Feedback

- Send your Feedback to [email protected]

Help Others, Please Share