Verilog ParametersIn Verilog, parameters are constants and do not belong to any other data type such as register or net data types. A constant expression refers to a constant number or previously defined parameter. We cannot modify parameter values at runtime, but we can modify a parameter value using the defparam statement. The defparam statement can modify parameters only at the compilation time. Parameter values can be modified using # delay specification with module instantiation. In Verilog, there are two methods to override a module parameter value during a module instantiation.

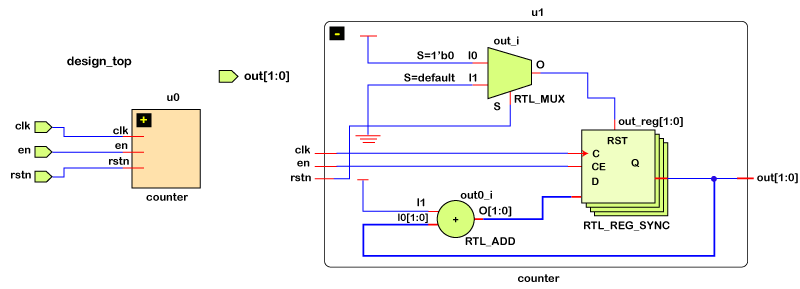

After the defparam keyword, the hierarchical path is specified to the parameter and the parameter's new value. This new value should be a constant expression. If the right-hand side expression references any parameters, it should be declared within the module where defparam is invoked. The module instance parameter value assignment method seems like an assignment of delay to gate instance. This method overrides parameters inside instantiated modules as they appear in the module. Using this format, parameters cannot be skipped. Constant expressions can contain previously declared parameters. When changes are detected on the previously declared parameters, all parameters that depend on this value are updated automatically. Consider, a 4-bit adder can be parameterized to accept a value for the number of bits, and new parameter values can be passed during module instantiation. So, an N-bit adder converts into a 4-bit, 8-bit or 16-bit adder. They are like arguments to a function that is passed during a function call. There are two types of parameters, module and specify, and both accept a range specification. But, they are made as wide as the value to be stored them, and hence a range specification is not necessary. Module parametersIt can be used to override parameter definitions within a module and makes the module have a different set of parameters at compile time. A parameter can be modified with the defparam statement. It is common to use uppercase letters in names for the parameter to notice them instantly. The below module uses parameters to specify the bus width, data width and the depth of FIFO within the design, and can be overridden with new values when the module is instantiated or by using defparam statements. In the new ANSI style of Verilog port declaration, we may declare parameters such as: Overriding parametersParameters can be overridden with new values during module instantiation. The first part is the module called design_ip by the name d0 where new parameters are passed within # ( ). The second part is use a Verilog construct called defparam to set the new parameter values. The first method is commonly used to pass new parameters in RTL designs. And the second method is used in testbench simulations to quickly update the design parameters without having to reinstantiate the module. The module counter has two parameters N and DOWN, which is declared to have a default value of 2 and 0. N controls the number of bits in the output, effectively controlling the width of the counter. It is a 2-bit counter by default. Parameter DOWN controls whether the counter should increment or decrement. The counter will decrement because the parameter is set to 0. 2-bit up Counter The module counter is instantiated with N as 2 even though it is not required because the default value is anyway 2. DOWN is not passed during module instantiation. And it takes the default value of 0 making it an up-counter. The default parameters are used to implement the counter where N equals two, making it a 2-bit counter, and DOWN equals zero, making it an up-counter. The output from the counter is left unconnected at the top level.

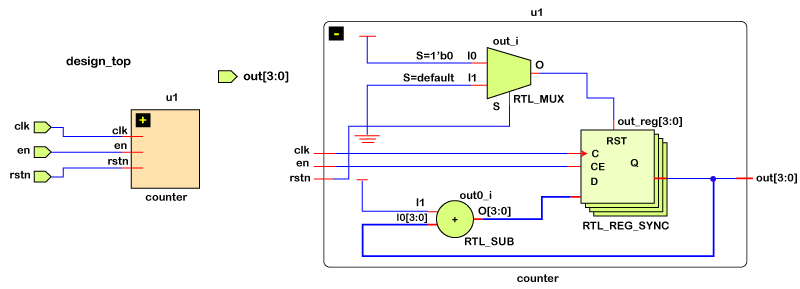

4-bit down Counter In this case, the module counter is instantiated with N as 4 making it a 4-bit counter. DOWN is passed a value of 1 during the module instantiation and hence a down-counter is implemented.

Specify ParametersThese parameters are used to provide time and delay values and declared using the specparam keyword. It is allowed to use both within the specified block and the main module body. Difference between Specify and Module Parameters

Notes Here are some important notes for the Verilog parameters, such as:

Next TopicVerilog Timing Control

|

For Videos Join Our Youtube Channel: Join Now

For Videos Join Our Youtube Channel: Join Now

Feedback

- Send your Feedback to [email protected]

Help Others, Please Share