EHCI

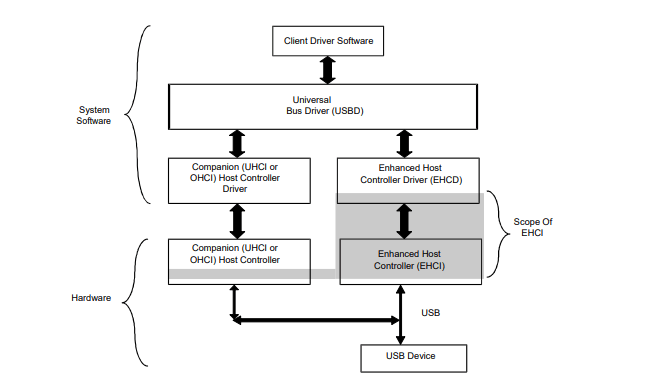

EHCI stands for Enhanced Host Controller Interface and is responsible for defining the register-level interface of the host controller of USB 2.0. it specifies both the hardware and software interface between the software of your system and the controller hardware. It acts as a bridge between the hardware of the controller and the system software. The specification is defined for the system builders and system driver developers. To understand the specification, the reader should know about USB 2.0 Specifications. There are certain conflicts between the provided version specification and the USB 2. specifications. But in case of any conflicts, precedence is given to the USB 2.0 specification. The reader must be familiar with the Universal Serial Bus Specification, Revision 2.0. Despite due diligence, there may exist conflicts between this specification and the USB 2.0 Specification. USB 2.0 Host ControllerThe companion host controller can be any USB 1.1 host controller. It can either be OHCI or UHC. The companion host controller handles both full and low-speed USB devices. These devices should be connected to the root ports of the system. The cHCs don't know about the working of the high-speed mode host controller. The high-speed devices are maintained and managed by the EHCI host controller. They can be included in a USB 2.0 host controller without changing. When the eHC was executed and configured, the host controller was assigned as the owner of all the root ports in the system. The eHC and the drivers of the host controllers find all the attached devices. It also includes extra control bits that can be seen in each port register that handles the routing logic. As discussed, the drivers' ownership is primarily given to the eHC. When the device is not a high-speed device, the eHC drivers release the ownership of this device. The control of the device is released, and ownership is assigned to a companion host controller. For the particular port, enumeration begins from the initial point of attachment. The device connected to this point is enumerated under the companion host controller. Otherwise, eHC retains the port ownership. Then the enumeration is done under the eHC. The USB 2.0 specifications do not provide descriptions for both UHCI and OHCI. It defines the register and schedule interface to the EHCI. The key features provided by the Enhanced Host Controller Interface are as follows:

General Architecture of Enhanced Host Controller Interface

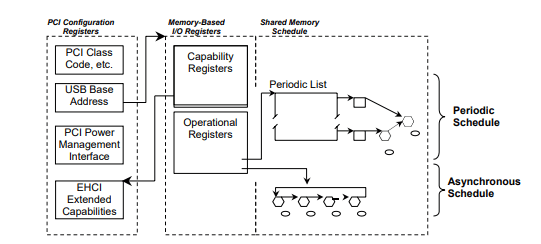

The schedule interface in EHCI has separate schedules for each category of transfer type mentioned above. The EHCI provides support for both asynchronous transfer and periodic transfer. The periodic transfer supported by the EHCI includes both isochronous and interrupt, while the asynchronous transfer supported by EHCI includes control and bulk type transfer. The periodic schedule is a time-based frame list that resembles a sliding window of time of the controller items. Both types of periodic transfer that is, isochronous and interrupt transfers, are facilitated by the periodic schedule. The asynchronous schedule is a circular list of work items that implements round-robin service to all the asynchronous transfers. The software can also start or stop any schedule using the EHCI. This allows the software to keep the USB alive with SOF traffic. When the EHCI disables both schedules, the controller won't be able to access the scheduled space. Thus, the host controller cannot access the main memory with both schedules disabled. This allows mobile systems the better utilization of CPU power. The internal architecture of EHCIThe Enhanced Host Controller Interface defines three spaces of the interface:

EHCI Schedule Data StructuresThe Enhanced Host Controller Interface handles and controls the interrupt, bulk, and control transfer types. It uses a simple buffer to queue the data structure. It uses the queue data structure to facilitate automatic, in-order data transfer streaming. It enables the software to add the data buffers asynchronously to the queue, which maintains continuous streaming. USB-defined short packet semantics are supported on all the processing boundary conditions. This does not require any additional intervention from the software. The split transaction is used for both full and low-speed non-isochronous transfers. The split transactions are handled as a simple extension of the high-speed model. The same data structures also handle them. User interface data structures control the full and high-speed isochronous transfers. Root Hub EmulationA host controller must use a port hub. The operational register space has the port registers that include the minimum hardware status and control required to handle each port register within the USB specification. The host controller moves through the EHCI schedules and encounters the work items. This results in the host controllers implementing the USB transactions. The transactions are shared with all the root ports enabled and connected to downstream USB devices. The port register provides the control and status report needed to manipulate the port with respect to the USB specification.

Next TopicCache Memory and Virtual Memory

|

For Videos Join Our Youtube Channel: Join Now

For Videos Join Our Youtube Channel: Join Now

Feedback

- Send your Feedback to [email protected]

Help Others, Please Share