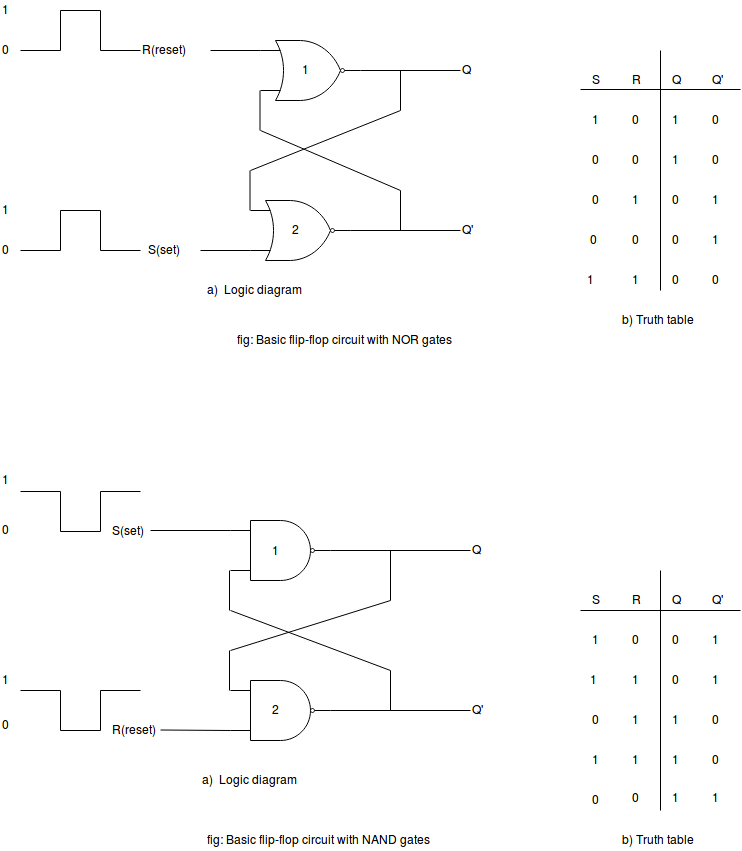

S-R Flip-flop/Basic Flip-FlopFlip flops are an application of logic gates. A flip-flop circuit can remain in a binary state indefinitely (as long as power is delivered to the circuit) until directed by an input signal to switch states. S-R flip-flop stands for SET-RESET flip-flops. The SET-RESET flip-flop consists of two NOR gates and also two NAND gates. These flip-flops are also called S-R Latch. The design of these flip flops also includes two inputs, called the SET [S] and RESET [R]. There are also two outputs, Q and Q'.

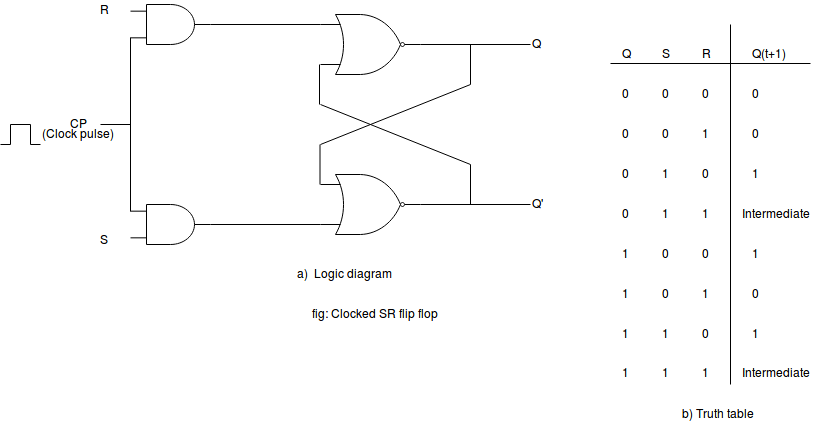

Clocked S-R Flip-FlopThe operation of a basic flip-flop can be modified by providing an additional control input that determines when the state of the circuit is to be changed. The limitation with a S-R flip-flop using NOR and NAND gate is the invalid state. This problem can be overcome by using a stable SR flip-flop that can change outputs when certain invalid states are met, regardless of the condition of either the Set or the Reset inputs.

A clock pulse is given to the inputs of the AND Gate. If the value of the clock pulse is '0', the outputs of both the AND Gates remain '0'.

Next TopicD Flip-Flop

|

For Videos Join Our Youtube Channel: Join Now

For Videos Join Our Youtube Channel: Join Now

Feedback

- Send your Feedback to [email protected]

Help Others, Please Share