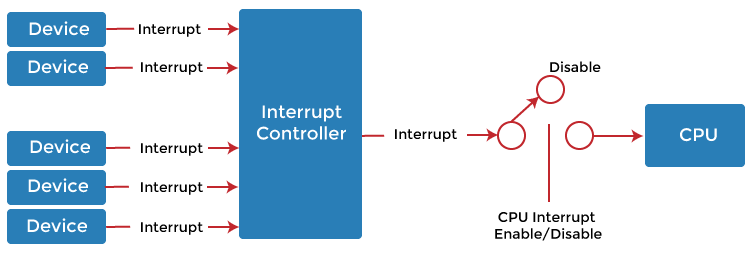

What is Interrupt in OS?An interrupt is a signal emitted by hardware or software when a process or an event needs immediate attention. It alerts the processor to a high-priority process requiring interruption of the current working process. In I/O devices, one of the bus control lines is dedicated for this purpose and is called the Interrupt Service Routine (ISR). When a device raises an interrupt at the process, the processor first completes the execution of an instruction. Then it loads the Program Counter (PC) with the address of the first instruction of the ISR. Before loading the program counter with the address, the address of the interrupted instruction is moved to a temporary location. Therefore, after handling the interrupt, the processor can continue with the process. While the processor is handling the interrupts, it must inform the device that its request has been recognized to stop sending the interrupt request signal. Also, saving the registers so that the interrupted process can be restored in the future increases the delay between the time an interrupt is received and the start of the execution of the ISR. This is called Interrupt Latency.

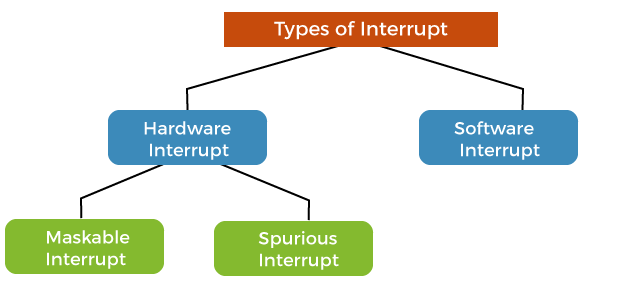

A single computer can perform only one computer instruction at a time. But, because it can be interrupted, it can manage how programs or sets of instructions will be performed. This is known as multitasking. It allows the user to do many different things simultaneously, and the computer turns to manage the programs that the user starts. Of course, the computer operates at speeds that make it seem like all user tasks are being performed simultaneously. An operating system usually has some code that is called an interrupt handler. The interrupt handler prioritizes the interrupts and saves them in a queue if more than one is waiting to be handled. The operating system has another little program called a scheduler that figures out which program to control next. Types of InterruptInterrupt signals may be issued in response to hardware or software events. These are classified as hardware interrupts or software interrupts, respectively.

1. Hardware InterruptsA hardware interrupt is a condition related to the state of the hardware that may be signaled by an external hardware device, e.g., an interrupt request (IRQ) line on a PC, or detected by devices embedded in processor logic to communicate that the device needs attention from the operating system. For example, pressing a keyboard key or moving a mouse triggers hardware interrupts that cause the processor to read the keystroke or mouse position. Hardware interrupts can arrive asynchronously for the processor clock and at any time during instruction execution. Consequently, all hardware interrupt signals are conditioned by synchronizing them to the processor clock and act only at instruction execution boundaries. In many systems, each device is associated with a particular IRQ signal. This makes it possible to quickly determine which hardware device is requesting service and expedite servicing of that device. On some older systems, all interrupts went to the same location, and the OS used specialized instruction to determine the highest priority unmasked interrupt outstanding. On contemporary systems, there is generally a distinct interrupt routine for each type of interrupt or each interrupts source, often implemented as one or more interrupt vector tables. Hardware interrupts are further classified into two types, such as:

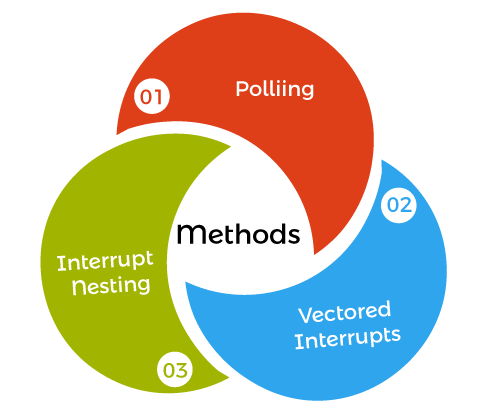

2. Software InterruptsThe processor requests a software interrupt upon executing particular instructions or when certain conditions are met. Every software interrupt signal is associated with a particular interrupt handler. A software interrupt may be intentionally caused by executing a special instruction that invokes an interrupt when executed by design. Such instructions function similarly to subroutine calls and are used for various purposes, such as requesting operating system services and interacting with device drivers. Software interrupts may also be unexpectedly triggered by program execution errors. These interrupts are typically called traps or exceptions. Handling Multiple DevicesWhen more than one device raises an interrupt request signal, additional information is needed to decide which device to consider first. The following methods are used to decide which device to select first,

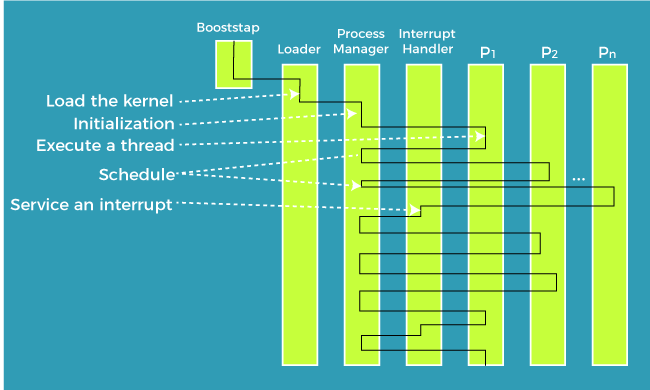

Interrupt HandlingWe know that the instruction cycle consists of fetch, decode, execute and read/write functions. After every instruction cycle, the processor will check for interrupts to be processed. If there is no interrupt in the system, it will go for the next instruction cycle, given by the instruction register. If there is an interrupt present, then it will trigger the interrupt handler. The handler will stop the present instruction that is processing and save its configuration in a register and load the program counter of the interrupt from a location given by the interrupt vector table. After processing the interrupt by the processor, the interrupt handler will load the instruction and its configuration from the saved register. The process will start its processing where it's left. This saves the old instruction processing configuration, and loading the new interrupt configuration is also called context switching. There are different types of interrupt handlers.

The interrupt handler is also called an interrupt service routine (ISR). The main features of the ISR are

Interrupt LatencyWhen an interrupt occurs, the service of the interrupt by executing the ISR may not start immediately by context switching. The time interval between the occurrence of interrupt and the start of execution of the ISR is called interrupt latency.

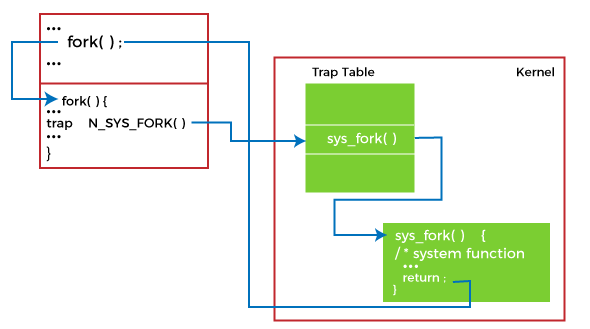

How CPU Response to InterruptsA key point towards understanding how operating systems work understands what the CPU does when an interrupt occurs. The CPU hardware does the same for each interrupt, allowing operating systems to take control away from the currently running user process. The switching of running processes to execute code from the OS kernel is called a context switch. CPUs rely on the data contained in a couple of registers to handle interrupts correctly. One register holds a pointer to the process control block of the currently running process, and this register is set each time a process is loaded into memory. The other register holds a pointer to a table containing pointers to the instructions in the OS kernel for interrupt handlers and system calls. The value in this register and contents of the table are set when the operating system is initialized at boot time. The CPU performs the following actions in response to an interrupt:

The CPU uses a table and the interrupt vector to find OS the code to execute in response to interrupts. A software interrupt is shown in the below image.

As the computer runs, processing switches between user processes and the operating system as hardware and software interrupts are received. Triggering MethodsEach interrupts signal input is designed to be triggered by either a logic signal level or a particular signal edge (level transition). Level-sensitive inputs continuously request processor service so long as a particular (high or low) logic level is applied to the input. Edge-sensitive inputs react to signal edges: a particular (rising or falling) edge will cause a service request to be latched. The processor resets the latch when the interrupt handler executes.

1. Level-triggeredA level-triggered interrupt is requested by holding the interrupt signal at its particular (high or low) active logic level. A device invokes a level-triggered interrupt by driving the signal to and holding it at the active level. It negates the signal when the processor commands it, typically after the device has been serviced. The processor samples the interrupt input signal during each instruction cycle. The processor will recognize the interrupt request if the signal is asserted when sampling occurs. Level-triggered inputs allow multiple devices to share a common interrupt signal via wired-OR connections. The processor polls to determine which devices are requesting service. After servicing a device, the processor may again poll and, if necessary, service other devices before exiting the ISR. 2. Edge-triggeredAn edge-triggered interrupt is an interrupt signaled by a level transition on the interrupt line, either a falling edge (high to low) or a rising edge (low to high). A device wishing to signal an interrupt drives a pulse onto the line and releases it to its inactive state. If the pulse is too short to be detected by polled I/O, then special hardware may be required to detect it. |

For Videos Join Our Youtube Channel: Join Now

For Videos Join Our Youtube Channel: Join Now

Feedback

- Send your Feedback to [email protected]

Help Others, Please Share